Table of Contents

Introduction

Longer filters create a bottleneck in a DSP assembly line. Minimizing filter length reduces the size of the bottleneck which allows the receiver to run at a faster sampling rate and therefore process more bandwidth. Minimizing filter length is important because it minimizes the number of multiplies that have to be performed. Multiplication can be slow and cause a heavy computational load.

Other blogs explaining the “why” of DSP:

Radio Receiver as an Assembly Line

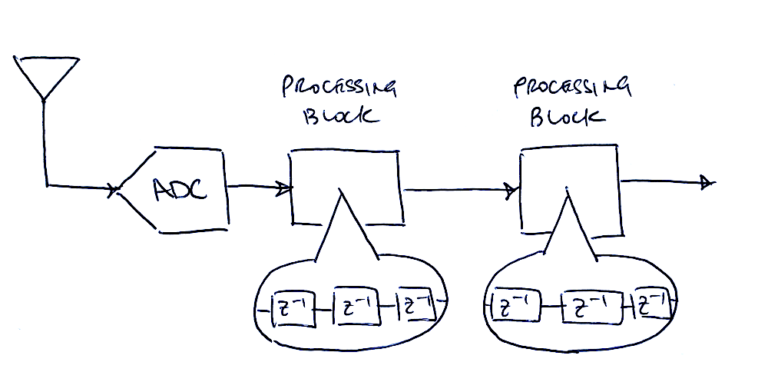

A digital radio receiver is similar to an assembly line. Electromagnetic waves are received by the antenna and then digitized by an analog to digital converter (ADC). Samples slowly move their way from the beginning of the assembly line, or the tapped delay line, to the end where they are finally demodulated. The samples are modified and processed by different operations along the way.

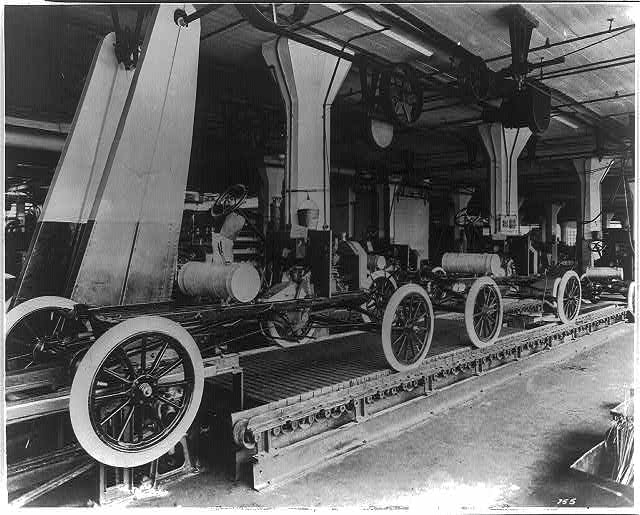

The same is true of an assembly line building cars. A conveyor belt is used to move a chassis through a factory which allows workers to operate and build the car over time. The product is constructed and improved by each subsequent operation in the assembly line.

Filtering Bottlenecks

How do you compute the performance of an assembly line? One metric would be the number of cars that can be produced per day.

Consider the example of an assembly line which needs to produce 10 cars a day. The factory can supply 10 chassis, can attach 10 steering wheels a day, but can only attach 8 doors per day. The whole assembly line will now run at 8 cars per day due to the processing bottleneck. The speed of the car assembly line can be represented as a frequency, 8 cars per day, or as the time period to produce the car, which is 1 hour per car.

The radio receiver sampling rate is the speed at which it can process samples, where as the sampling period is how long it takes for a sample to be processed before being sent to the next operation. The sampling frequency ![]() and sampling period

and sampling period ![]() are inverses of one another,

are inverses of one another,

(1) ![]()

Consider a case in which the ADC produces 1 sample every 1 microseconds but a follow-on filtering operation can only operate on and produce 1 sample every 4 microseconds. The filtering operation is the bottleneck and reduces the sample rate from ![]() to

to ![]() .

.

Filtering can become a processing bottleneck for DSP receivers. Longer filters require more computations which take more time to process and slow down the sample rate assembly line.

Therefore reducing the processing time for each sample, which is the sampling period ![]() , increases the sampling frequency

, increases the sampling frequency ![]() . A large sampling frequency means more bandwidth that your receiver can process. More bandwidth equals more customers, more sales and more success.

. A large sampling frequency means more bandwidth that your receiver can process. More bandwidth equals more customers, more sales and more success.

Computations to Multiply

In general, computing and mathematics in general take more clock cycles to complete than statements and relational operators. For example, if-else statements, case statements and relational operators such as ![]() and

and ![]() can be done much faster than multiplication which can take multiple clock cycles to implement.

can be done much faster than multiplication which can take multiple clock cycles to implement.

Let’s take a look at what’s required to implement a multiply. The multiplication of a real number ![]() against a complex number

against a complex number ![]() requires two multiplications,

requires two multiplications,

(2) ![]()

Every number in DSP is going to be represented by a certain number of B bits. A B bit real multiply requires B binary additions to be implemented. As an example, consider the system is using the standard B=16 bits to represent numbers. The multiplication in (2) requires two real multiplies, and each multiply requires B=16 additions, for a total of 2B = 32 total additions.

Now consider a filter of real weights with length L being applied to a complex signal. The filter will have to implement 2L real multiplies which requires 2BL multiplies. For even a small length filter the amount of computation can grow substantially. For a filter length of L=8, each output sample requires ![]() additions.

additions.

Now consider that your sampling rate is ![]() . Your L length filter applied to B bit complex samples will require

. Your L length filter applied to B bit complex samples will require ![]() million additions per second!

million additions per second!

The following video does a great job explaining all of the computation needed to implement one multiply in hardware:

The problem is that multiplies are so slow because they require so much computation! Reducing the multiplies is the motivation for folding FIR filter weights as described in this post.

Benefits of Minimizing Filter Length

A longer filter will give better performance: more sidelobe attenuation, shorter transition bandwidths and less passband ripple. Why minimize filter length?

A major marketing factor for a radio receiver is the amount of bandwidth it can process. Consider and example in which you are buying a WiFi router. One model has a smaller bandwidth and can only deliver blurry video, whereas the other model can deliver full high definition streaming video. Which do you choose?

Another practical consideration is that while longer filters have better performance they also require:

- more expensive chips to handle the processing,

- more power to supply the computing hardware,

- more heat since they are doing more computation,

- larger physical size.

Conclusion

Longer filters create processing bottlenecks which reduces the sampling rate of the radio receiver. Filters can become bottlenecks because the multiplies require a significant amount of computation to implement. Minimizing filter length reduces the multiplies, removes bottlenecks and allows the radio receiver to process more bandwidth.

Other blogs explaining the “why” of DSP: